# **МИКРОПРОЦЕССОРЫ**

В 3 книгах

Книга 2

# СРЕДСТВА СОПРЯЖЕНИЯ

## КОНТРОЛИРУЮЩИЕ И ИНФОРМАЦИОННО-УПРАВЛЯЮЩИЕ СИСТЕМЫ

Под редакцией члена-корреспондента АН СССР Л. Н. ПРЕСНУХИНА

Допущено Министерством высшего и среднего специального образования СССР в качестве учебника для студентов высших технических учебных заведений

МИНСК «ВЫШЭЙШАЯ ШКОЛА» 1987 ББК 32.973.2 я73 M59 УДК 681.325.5:621.382.049.77 (075.8)

Печатается по изданию:

Микропроцессоры. В 3 кн. Кн. 2. Средства сопряжения. Контролирующие и информационно-управляющие системы.— М.: Высш. шк., 1986.

Авторы: В. Д. Вернер, Н. В. Воробьев, А. В. Горячев, Г. И. Фролов, А. А. Шишкевич.

Рецензент — кафедра автоматизированных систем управления МВТУ им. Н. Э. Баумана (зав. кафедрой — проф. В. Н. Четвериков)

Микропроцессоры: В 3 кн. Кн. 2: Средства сопряжения. М 59 Контролирующие и информационно-управляющие системы: Учеб. для техн. вузов / В. Д. Вернер, Н. В. Воробьев, А. В. Горячев и др.; Под ред. Л. Н. Преснухина.— Мн.: Выш. шк., 1987.— 303 с.: ил.

Учебник является второй книгой из серии, выпускаемой под общим названием «Микропроцессоры». В нем рассмотрены вопросы схемотехники и организации связей элементов и узлов микро-ЭВМ; аппаратурные средства сопряжения систем сбора и преобразования информации, вопросы теории и проектирования информационно-управляющих вычислительных систем (ИУВС) на базе микроЭВМ с изложеннем материалов математического обеспечения и организации вычислитель ного процесса специализированных ИУВС.

Впервые книга вышла в издательстве «Высшая школа» (Москва) в 1986 г.

$$M\frac{2405000000-151}{M304(03)-87}40-87$$

ББК 32.973.2я73

- © Издательство «Высшая школа», 1986.

- © Оформление. Издательство «Вышэйшая школа», 1987.

#### **ВВЕДЕНИЕ**

Научно-технический прогресс, определяющий мощный подъем общественного производства, в значительной степени обусловлен широким внедрением достижений электроники во все отрасли народного хозяйства. Прогресс в области вычислительной техники и радиоэлектроники связан с достижениями микроэлектроники в создании интегральных схем малой, средней, большой и сверхбольшой степени интеграции. Появление микропроцессорных БИС позволило из-за их дешевизны, малых габаритов, массы, мощности потребления и свойства программируемости функций решить проблему разработки малого числа БИС для большого числа применений, внедрить вычислительную технику в те области, в которых ранее она не использовалась.

Необходимость повышения технического уровня вычислительной техники, приборов и средств автоматизации, связи, робототехники на основе новейших достижений микроэлектроники специально отмечалась в директивных документах партии и правительства.

Промышленностью освоены и выпускаются много типов микропроцессоров, благодаря которым обеспечены исключительные преимущества цифровым методам обработки информации. Однако существуют аналоговые сигналы, которые надо принимать, обрабатывать, хранить и выдавать пользователю. Важное значение приобретает проблема связи аналоговых объектов с цифровыми управляющими машинами, в частности вопросы преобразований, нормализации сигналов, методы и средства передачи аналоговых сигналов по линиям связи при наличии помех и т. д. Применение микропроцессоров и микроЭВМ для сбора данных и управления производственными процессами вызывает ряд проблем аналого-цифрового преобразования сигналов, которые должен решать пользователь.

Для обработки аналоговых и цифровых сигналов разработана большая номенклатура микросхем, среди которых можно отметить генераторы, усилители, аналого-цифровые и цифроаналоговые преобразователи, модуляторы, компараторы, переключатели тока и напряжения, элементы выборки и хранения, фильтры, вторичные источники питания, центральные процессорные элементы, устройства управления вводом-выводом, программируемые параллельные и последовательные интерфейсы, контроллеры прямого доступа к памяти, магистральные приемопередатчики, блоки микропрограммного управления, приоритетного прерывания, арифметические расширители, запоминающие устройства, многофункциональные синхронизирующие устройства, программируемые таймеры и т. п.

Большинство перечисленных схем и устройств являются функциональными составными частями микропроцессорных комплектов, в значительной степени определяя архитектуру микроЭВМ. Однако практически любая микроЭВМ, кроме основных функциональных БИС, содержит и значительное число микросхем малой и средней степени интеграции (табл. В.1), особенно в периферийном оборудовании, датчиках первичной информации, устройствах встроенного контроля и диагностики, устройствах отображения информации и т. д.

Учебник в основном будет посвящен возможностям использования схем средней степени интеграции, большинство из которых можно рассматривать как многофункциональные узлы (см. уровень межрегистровых передач в табл. В.1). Излагаемый материал подкрепляется примерами применения отечественных микросхем для обработки аналоговых и цифровых сигналов, в ряде случаев дается расчет ана-

лизируемых схем.

Контроль сложных изделий — трудоемкий и длительный процесс, требующий усилий большого числа лиц для получения достоверной информации. Системы контроля на базе микроЭВМ обладают большими преимуществами в отношении стоимости контроля, уменьшения времени его проведения и обработки результатов, надежности, обеспечивают значительную гибкость, высокую компактность и модульную простоту, а также открывают широкие возможности для новых приложений, ранее требовавших использования дорогих специализированных ЭВМ.

В основу решения задачи автоматизированного контроля технического состояния объектов положены следующие принципы: максимальная степень автоматизации процесса контроля и сведение к минимуму числа ручных операций, повышение достоверности резуль-

Таблица В. 1

| Уровень                        | Составные части                         |                                                                                                                                 |  |  |

|--------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| нерархии                       | Система                                 | Элементы системы                                                                                                                |  |  |

| Системный                      | Вычислительная си-<br>стема, ЭВМ        | Устройства ЭВМ (АУ, УУ,<br>ОЗУ, ПЗУ, УВВ, каналы свя-                                                                           |  |  |

| Уровень межрегистровых передач | Устройства ЭВМ                          | зи,)<br>Узлы ЭВМ (сумматоры, счетчики, регистры, дешифраторы,<br>АЦП, ЦАП,)                                                     |  |  |

| Уровень логических<br>схем     | Узлы ЭВМ                                | Цифровые и аналоговые элементы ЭВМ (И, ИЛИ, И — НЕ, ИЛИ — НЕ, ИЛИ — НЕ,, триггеры, элементы ЗУ, операционные усилители, ключи,) |  |  |

| Схемотехнический               | Цифровые и аналого-<br>вые элементы ЭВМ | Электронные компоненты<br>(транзисторы, диоды, резисторы,                                                                       |  |  |

| Қомпонентный                   | Электронные компо-<br>ненты             | конденсаторы,) Материалы (магнитные материалы, металлы, полупроводники, диэлектрики,)                                           |  |  |

татов контроля, автоматическая выдача протокола результатов испытаний; высокая надежность системы, основанная на использовании встроенной микроЭВМ и модульной структуры; максимальная простота и доступность программного обеспечения, благодаря которым система контроля может обслуживаться лицами, не являющимися специалистами в области вычислительной техники.

В наибольшей степени этим требованиям отвечают одноплатные микроЭВМ «Электроника МС1201.01», обладающие высокой надежностью, обусловленной использованием интегральных микросхем высокой степени интеграции, широкими функциональными возможностями и развитым программным обеспечением, совместимым с рядом отечественных и зарубежных микро- и мини-ЭВМ (например, «Электроника 60», СМ-3, СМ-4, «Электроника 100-25», а также широко известное семейство мини- и микроЭВМ системы PDP-11).

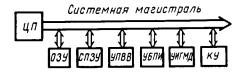

Магистрально-модульный принцип, положенный в основу организации этого семейства ЭВМ и распространенный на аппаратурные и программные средства, обеспечивает совместимость модулей на конструктивном, электрическом, функциональном и программном уровнях, однородность структуры, гибкость в выборе аппаратурных и программных модулей, возможность расширения структуры, модернизацию модулей и постоянное совершенствование системы в целом. Системы с общей магистралью хорошо приспособлены для работы в АСУТП, в системах информационно-измерительных, для автоматизации научных исследований, автоматизированного контроля (АСК), когда требуются высокая производительность, гибкость и работа в реальном масштабе времени.

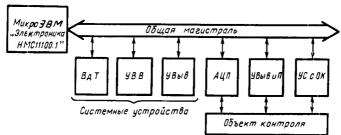

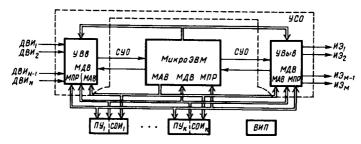

Стандартизация связей делает систему легко перестраиваемой в зависимости от предъявленных к ней требований и обеспечивает возможность ее расширения за счет подключения новых или замены старых внешних устройств ВУ. В качестве примера на рис. В.1 показана схема одной из возможных АСК с применением микроЭВМ и общей магистрали, где ВдТ — видеотерминал; УВВ — устройство вывода на печать; АЦП — аналого-цифровой преобразователь; УВыв и П — устройство вывода и приема релейных сигналов; УС с ОК — прочие устройства связи с объектом контроля. Ядром системы является микроЭВМ, выполняющая функции приема, обработки и передачи информации. Видеотерминал работает в качестве оперативного

Рис. В.1. Пример схемы автоматизированной системы контроля.

средства связи между человеком-оператором и системой контроля. Устройство ввода-вывода на перфоленту используется для ввода программ контроля в оперативную память микроЭВМ перед началом-работы, а также для вывода скорректированных программ. Для получения протокола результатов контроля объекта служит устройство

вывода на печать.

Для осуществления контроля параметров объект должен быть оснащен системой измерительных датчиков. Большинство датчиков преобразуют некоторую физическую величину в электрическую. Примерами датчиков с электрическими выходами являются термопары, терморезисторы для измерения температуры, тензодатчики для измерения давления или незначительного смещения, потенциометры для измерения положения и т. п. Сигнал на выходе датчика (напряжение или ток) необходимо преобразовать в форму, приемлемую для использования в ЭВМ. Такое преобразование выполняется с помощью различного рода аналого-цифровых преобразователей (АЦП).

Как показывает отечественный и зарубежный опыт, системы сопряжения с датчиками и приемниками информации, как правило, значительно превышают микроЭВМ по объему и стоимости электронного оборудования.

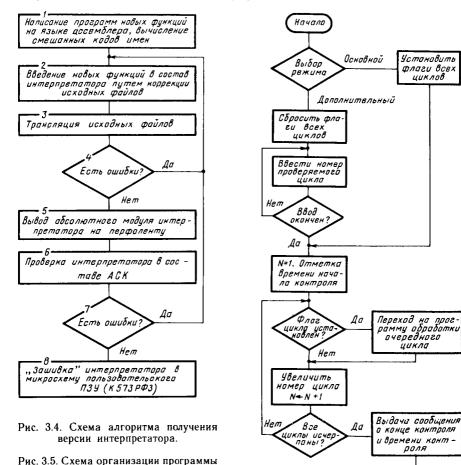

Реализация преимуществ автоматизированного контроля на основе микроЭВМ возможна в полной мере лишь при соответствующей организации программного обеспечения. Основное ограничение на использование микроЭВМ в АСК связано с необходимостью разрабатывать программное обеспечение для каждого конкретного применения. Одним из вариантов, позволяющих преодолеть трудности программирования, является применение диалоговых языков высокого уровня. В настоящей работе для автоматизированного контроля предлагается известный диалоговый язык программирования ФОКАЛ, расширенный и дополненный специальными функциями [1]. Выбор именно этого языка объясняется удачным сочетанием следующих его важных качеств: а) функциональная простота и гибкость, обеспечивающие эффективную реализацию программного обеспечения; б) наличие средств управления общей магистралью; в) простота, легкость изучения и использования; г) компактность интерпретатора языка и программ пользователя; д) возможность работы в режиме диалога.

Проектирование системы контроля — комплексная задача, требующая от инженера-разработчика глубоких знаний как в области создания аппаратурных средств, так и в области программного обеспечения. В существующей в настоящее время технической литературе вопросу единого подхода к описанию и проектированию аппаратурных и программных средств уделяется явно недостаточное внимание. Материал, излагаемый в книге, построен таким образом, чтобы всюду, где это возможно, прослеживалась связь между аппаратурным и программным обеспечением. Наряду с общими вопросами организации микроЭВМ, необходимыми для понимания функционирования всей системы, приводятся конкретные примеры написания про-

грамм связи с внешними устройствами на языке машинного уровня, дается представление об организации интерпретирующей программы, описана методика включения новых функций в состав интерпретатора, дается пример организации и написания управляющей

программы на языке высокого уровня.

Достигнутый отечественной электронной промышленностью высокий уровень технологии элементной базы средств вычислительной техники, характеризуемый производством спектра МПК БИС (табл. В.2), БИС запоминающих устройств (табл. В.3), БИС интерфейса, интегральных схем аналоговой и цифроаналоговой техники, в совокупности с новыми архитектурными решениями открывает широкие возможности к массовому созданию информационно-управляющих вычислительных систем с более совершенными тактико-техническими характеристиками.

Таблица В. 2

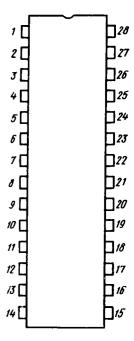

| Обо-<br>зна-<br>чение<br>МПК | Коли-<br>чество<br>БИС в<br>наборе | Раз-<br>ряд-<br>ность | Так-<br>товая<br>час-<br>тота,<br>МГц | Схемо-<br>техника | Система<br>команд | Напряжение<br>питания, В | Тип<br>корпуса |

|------------------------------|------------------------------------|-----------------------|---------------------------------------|-------------------|-------------------|--------------------------|----------------|

| KP580                        | 7                                  | 8                     | 0,5                                   | пΜДП              | Постоянная        | +5;+12;-5                | 2123.40-2      |

| K587                         | 4                                  | 4n                    | 0,5                                   | КМДП              | Произвольная      | +9                       | 429.42-1       |

| KP588                        | 5                                  | 16                    | 1,0                                   | кмдп              | Постоянная        | <b>∔</b> 5               | 2124.42 - 1    |

| K589                         | 9                                  | 2n                    | 6,0                                   | ТТЛДШ             | Произвольная      | +5                       |                |

| K1800                        | 4                                  | 4n                    | 36,0                                  | ЭСЛ               | »                 | -5,2;-2                  | 2207.48 - 1    |

| K1801                        | 3                                  | 16                    | 8,0                                   | nМДП              | Постоянная        | +5                       | 429.42-5       |

| KP1802                       | 6                                  | 8n                    | 8,0                                   | ТТЛДШ             | Произвольная      | +5                       | 2206.42-1      |

| KP1804                       | 6                                  | 4n                    | 8,0                                   | ттлдш             | »                 | +5                       | 2123.40—3      |

Таблипа В. 3

| <b>№</b><br>п/п | Обозна-<br>чение<br>БИС ЗУ | Тип ЗУ                     | Информа-<br>ционная<br>емкость      | Время<br>чтения<br>запи-<br>си, нс | Схемо-<br>техника   | Напряжение<br>питания, В | Мощ-<br>ность<br>потреб-<br>ления,<br>мВт/бит |

|-----------------|----------------------------|----------------------------|-------------------------------------|------------------------------------|---------------------|--------------------------|-----------------------------------------------|

| 1               | <b>К</b> 541РУ1            | ОЗУ ста-<br>тическое       | 4096×1                              | 400                                | И²Л                 | +5                       | 0,11                                          |

| 2               | <b>КР537РУ2</b>            | То же                      | 4096×1                              | 540                                | КМДП                | <del>+</del> 5           | 0,07                                          |

| 3               | Қ565РУ1                    | ОЗУ ди-<br>намиче-<br>ское | 4096 🔀 1                            | 400                                | nMДП                | +5<br>+5, $+12$ , $-5$   | 0,175                                         |

| 4<br>5          | Қ565РУЗ<br>Қ588РР11        | То же<br>ППЗУ              | $16384 \times 1$<br>$1024 \times 1$ | 700<br>500                         | <i>п</i> МДП<br>И²Л | +5, +12, -5<br>+5        | 0,03<br>0,3                                   |

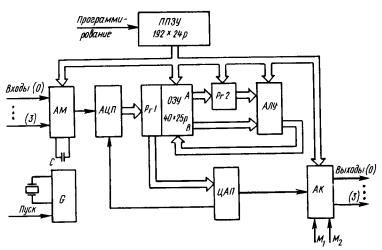

В данном учебнике под информационно-управляющей вычислительной системой (ИУВС) будем понимать комплекс аппаратурных и программных средств, который под воздействием оператора или автоматически управляет состоянием какого-либо объекта. Работа ИУВС при управлении реальными объектами связана, как правило, с необходимостью обмена информацией с большим числом внешних устройств, с решением многих задач в реальном масштабе времени при их относительной неизменности в течение всего времени эксплуатации, с большой продолжительностью непрерывной работы при

| SUMC (32) SCP-050             | 16/32/48 16/32<br>Плавающая точка<br>Нет данных Микрокомандное                 | 2.5 1<br>10,0 3<br>35,0 54 (32)<br>50 MII 50C,<br>KMJII/KHC        |             | 5 Нет данных<br>10 6                                                                      | 5,3 2,7   | ых Вероятность безог-<br>казной работы<br>0,8814 в течение<br>двух лет |

|-------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------|

| SUM                           |                                                                                | КМДП                                                               | 25          | _                                                                                         |           | Нет данных                                                             |

| MOD/LS1-10                    | 16/32/48<br>Плавающая точка<br>Нет данных                                      | 1,7<br>5,8<br>11,7<br>TTJ, BИС, СИС                                | 4K<br>256K  | 20                                                                                        | 7,7       | Нет данных                                                             |

| AP-101                        | 32 16/32/48<br>Плавающая точка Плавающая точка<br>Микрокомандное Нет данных    | 2,4<br>7,2<br>Нет данных<br>ТТЛ ИС                                 | 32K<br>256K | 16-разрядный мультиплексный канал<br>Нет данных                                           | 23,4      | Наработка на отказ Нет данных<br>1325 ч                                |

| 4P <sub>i</sub> /CP-2         | 16—32<br>Фиксированная точ-<br>ка<br>Микрокомандное                            | 5—10<br>19<br>47<br>TTA MC                                         | 8K<br>32K   | 16-разрядный муль-<br>типлексный канал<br>250                                             | 23        | Наработка на отказ<br>4000 ч                                           |

| Технические<br>характеристики | Формат операндов<br>Представление чисел<br>Управление<br>Время выполнения опе- | раций, мкс:<br>сложения<br>умножения<br>деления<br>Элементная база |             | Число каналов устрой-<br>ства ввода-вывода ин-<br>формации<br>Мощность потребления,<br>Вт | Масса, кг | Показатели надежности                                                  |

сохранении устойчивости к отказам. Это приводит к некоторым особенностям архитектуры (структуры и системного программного обеспечения) ИУВС по сравнению с универсальными средствами вычислительной техники.

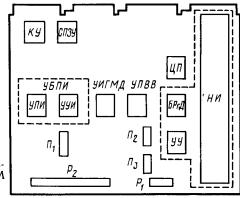

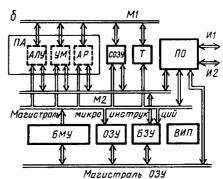

Из структурных особенностей ИУВС следует отметить: 1) развитую систему сопряжения с большим количеством внешних устройств (как правило, датчиков информации); 2) использование различного рода каналов ввода-вывода и стандартного интерфейса; 3) развитую систему средств управления и отображения информации; 4) возможность прерываний работы ИУВС; 5) специализацию системы команд, ориентированную на выполнение алгоритмов определенного класса; 6) развитую систему памяти (применение наряду с ОЗУ ПЗУ и ППЗУ большой информационной емкости и быстродействия); 7) наличие системы аппаратурного контроля; 8) наличие счетчиков реального времени.

Системное программное обеспечение ИУВС должно быть ориентировано на: 1) выполнение вычислений в реальном масштабе времени; 2) обеспечение обмена информацией во время решения задач; 3) большой объем используемых данных и прикладных программ; 4) большое количество операций логического преобразования, поиска и упорядочения информации; 5) использование программно-логических способов защиты как от сбоев и отказов ИУВС, так и от сбоев во входной информации.

Примерами задач, решаемых ИУВС, могут служить задачи: 1) управления электромеханическими устройствами в реальном масштабе времени; 2) обработки сигналов в системах связи; 3) селекции сигналов в условиях шумов; 4) коммутации сообщений; 5) сбора и отображения информации. В частности, по данным [2], решение задач последнего типа может потребовать ИУВС с производительностью  $40 \cdot 10^6$  операций/с и памятью  $10^9$  бит.

Некоторые технические характеристики (время выполнения команд, число команд, разрядность данных, габаритно-весовые и надежностные показатели) ряда зарубежных ЭВМ, применяемых в авиационно-космических ИУВС, приведены в табл. В.4. Анализ тенденций совершенствования вычислительных средств для ИУВС [2] показывает, что если раньше целесообразным считалось оптимизировать характеристики ЭВМ в соответствии с конкретными задачами ИУВС, то в настоящее время более перспективно использование в ИУВС ЭВМ универсального типа. Тем не менее в ИУВС, к которым предъявляются весьма жесткие требования по быстродействию, надежности, большое значение по-прежнему будут иметь специализированные ЭВМ.

В целом в проектировании ЭВМ ИУВС настоящего поколения проявляются следующие тенденции: 1) применение БИС микропроцессорных наборов, БИС ЗУ и нестандартных (заказных) ИС высокой степени интеграции; 2) микропрограммный принцип управления; 3) представление данных в форме с плавающей точкой, что на 50 % сокращает время подготовки задач; 4) приближение ЭВМ ИУВС к универсальным ЭВМ, которое выражается в использовании языков

высокого уровня, арифметических операций в форме с плавающей точкой, модульности конструкции и т. д.; 5) стандартизация ЭВМ для ИУВС; 6) переход к адаптивным самоорганизующимся структурам; 7) стандартизация системы команд; 8) модульность программного обеспечения.

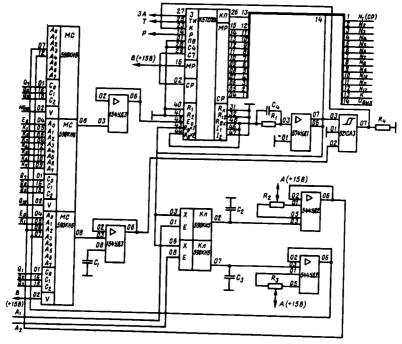

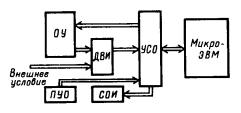

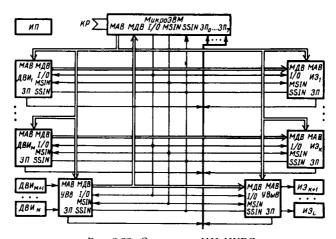

Примеры структурных решений ИУВС, построенных на базе микроЭВМ или БИС микропроцессорных наборов — в дальнейшем их будем называть микропроцессорными ИУВС (МП ИУВС), рассматриваются в § 2.3, однако необходимо отметить, что основу рассматриваемых МП ИУВС составляют одна или несколько микроЭВМ (микропроцессоров), устройство сопряжения с объектом, датчики входной информации и средства отображения информации и управления состоянием системы, предоставляемые оператору.

Авторы сделали попытку систематизировать имеющиеся в литературе рекомендации по проектированию МП ИУВС, поясняя их примерами из опыта собственных разработок МП ИУВС. В частности, предпринята попытка изложить методику назначения технических требований на разработку ИУВС при различных формах исходного задания; рассмотрены методика проектирования однопроцессорной ИУВС и архитектурные особенности и интерфейсы МП ИУВС; изложены методики оценки надежностных характеристик, рекомендации по конструированию ИУВС; описываются структурные и схемотехнические особенности построения ИУВС на базе МПК БИС серии К589.

Учитывая трудность выполнения поставленной задачи из-за многообразия подходов к созданию ИУВС в силу принципиальной зависимости ее архитектуры от класса решаемых ею задач, авторы понимают, что оно может служить лишь введением в проблему. Тем не менее они надеются, что для студентов втузов и для неспециалистов в области вычислительной техники, начинающих применять средства микропроцессорной вычислительной техники в ИУВС для народного хозяйства, учебник поможет разобраться в ключевых вопросах: с чего начать, как и какие технические вопросы необходимо решить.

## І. СХЕМОТЕХНИКА СРЕДСТВ СОПРЯЖЕНИЯ

Проектируя ту или иную систему с использованием микроЭВМ, необходимо рассмотреть особенности схемотехники цифровых и аналоговых элементов сопряжения, а также схемы средней степени интеграции, являющиеся многофункциональными узлами ЭВМ. В разделе разбираются варианты структур устройств сопряжения с объектом, в том числе на базе аналого-цифрового микропроцессора; даются классификация и примеры организации интерфейсов; обсуждаются характеристики датчиков первичной информации.

#### 1. СРЕДСТВА СОПРЯЖЕНИЯ МИКРОЭВМ С ОБЪЕКТОМ

# 1.1. Средства автоматического ввода и вывода данных в системах сбора и обработки информации

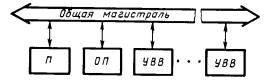

Структура устройств автоматического ввода данных. Рост сложности объектов управления, контроля, измерения, совершенствование технологических процессов обусловили необходимость высокой степени автоматизации процессов вычисления параметров управления, проведения процедур контроля, измерения элементов технологических процессов. Все эти различные по своей физической сущности задачи могут быть решены на основе использования автоматизированных систем сбора и обработки данных (система СОД). Основная тенденция проектирования современных СОД направлена на создание децентрализованных конфигураций систем, которые базируются на применении в качестве аппаратуры обработки данных МП или миниЭВМ.

Технические средства для реализации автоматизированных систем СОД должны содержать комплекс устройств, реализующих задачу ввода информации в МП без участия человека-оператора. Эта задача решается на основе введения датчиков первичной информации для преобразования неэлектрических величин в пропорциональные электрические. На основе изложенного можно сказать, что автоматизированная система сбора и обработки данных представляет собой сложное техническое устройство, которое в наиболее общем случае осуществляет автоматическое вычисление совокупных параметров управления, контроля, измерения объектов, различных по своей физической сущности, и регистрацию результатов вычислений.

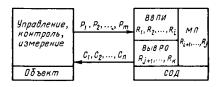

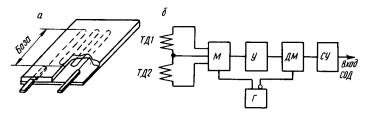

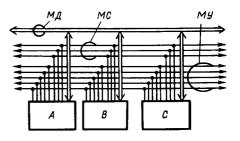

Характерные особенности системы СОД целесообразно рассмотреть во взаимодействии с объектом (рис. 1.1).

Целью проведения процедур сбора и обработки данных являются получение достоверной информации о состоянии объекта и рациональная организация процессов управления, контроля, измерения с высокими качественными характеристиками. Действительное качество процесса полностью определяется множеством параметров  $P_1$ ,

Рис. 1.1. Обобщенная структура связей объекта и системы СОД.

$P_2$ , ...,  $P_m$  объекта, числовое значение которых формирует объем первичной информации, поступающей на вход МП посредством блока ввода первичной информации ВвПИ, решающего задачу сбора данных. Множество возможных манипуляций с объектом (различные варианты контрольных процедур, управления, измерения) предполагает необходимость организации обратных связей для воздействия на объект сигналами  $C_1$ ,  $C_2$ , ...,  $C_n$  манипуляции внутренним состоянием объекта, которые формируются блоком вывода результатов обработки ВывРО. Сигналы внутреннего состояния системы СОД  $\Gamma_1$ ,  $\Gamma_2$ , ...,  $\Gamma_k$  также формируются и регистрируются блоком ВывРО.

В зависимости от целевого взаимодействия объекта и СОД возможны различные варианты формирования обобщенного математического выражения связей объекта и системы СОД.

Например,

$$C_{1} = F_{1}(P_{1} \ P_{2}, ..., P_{m}, r_{1}, r_{2}, ..., r_{k});$$

$$C_{2} = F_{2}(P_{1}, P_{2}, ..., P_{m}, r_{1}, r_{2}, ..., r_{k});$$

$$... ... ... ... ...$$

$$C_{n} = F_{n}(P_{1}, P_{2}, ..., P_{m}, r_{1}, r_{2}, ..., r_{k}).$$

$$(1.1)$$

$$P_{1} = f_{1}(C_{1}, C_{2}, ..., C_{n}, r_{1}, r_{2}, ..., r_{k});$$

$$P_{2} = f_{2}(C_{1}, C_{2}, ..., C_{n}, r_{1}, r_{2}, ..., r_{k});$$

$$...$$

$$P_{m} = f_{m}(C_{1}, C_{2}, ..., C_{n}, r_{1}, r_{2}, ..., r_{k}).$$

$$(1.2)$$

$$r_{1} = \varphi_{1}(P_{1}, P_{2}, ..., P_{m});$$

$$r_{2} = \varphi_{2}(P_{1}, P_{2}, ..., P_{m});$$

$$\vdots \qquad \vdots \qquad \vdots \qquad \vdots$$

$$r_{k} = \varphi_{k}(P_{1}, P_{2}, ..., P_{m}).$$

$$(1.3)$$

Выражение (1.1) определяет манипуляцию управления объектом, а функции  $F_1$ ,  $F_2$ , ...,  $F_n$  формируют алгоритм управления. Выражение (1.2) является обобщенной математической зависимостью процедуры контроля объекта, где функции  $f_1$ ,  $f_2$ , ...,  $f_n$  характеризуют различные внешние проявления свойств (внутреннего состояния) объекта контроля. Выражение (1.3) дает возможность решить задачу

самоконтроля СОД, а функциональные зависимости  $\varphi_1, \ \varphi_2, \ ..., \ \varphi_k$

образуют контрольные тесты СОД.

Обычно совокупность допустимых значений  $C_1, C_2, ..., C_n; P_1, P_2 ...,$  $P_m$ ;  $r_1, r_2, ..., r_k$  интерпретируют как многомерное пространство (Cмерное, Р-мерное, r-мерное), в пределах которого существование объекта и системы СОД имеет практическую ценность. В этом случае сочетание произвольно заданных значений  $C_i$ ,  $P_i$ ,  $r_i$  представляет собой координаты вектора многомерного пространства, что позволяет использовать для математического выражения связей объекта и системы СОД элементы матричного исчисления. В результате анализа математического выражения связей возможно рациональное построение структуры системы сбора данных, зависящей от конкретных условий задачи анализа. Однако в общем случае, исходя из требования ввода информации в МП, она должна содержать: группу датчиков первичной информации, размещенных в непосредственной близости от объекта управления, контроля или измерения, блок преобразователей аналоговых сигналов датчика в цифровые коды (АЦП), цифровые и аналоговые коммутаторы, аналоговые вычислительные устройства, цифровые и аналоговые каналы связи, блок преобразователей цифровых сигналов в аналоговые (ЦАП), цифровые регистрирующие устройства.

Различные требования по стоимостным и техническим характеристикам, предъявляемые к СОД, определяют возможность вариаций структуры СОД на основе выбора метода обработки сигналов.

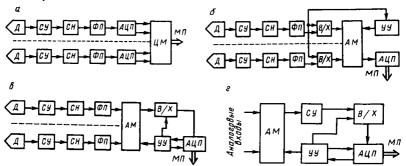

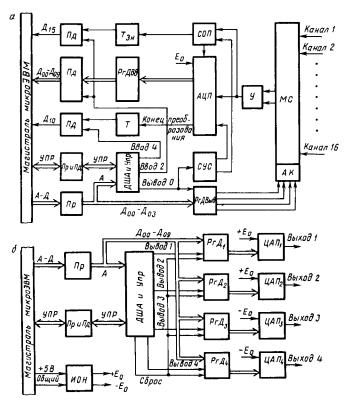

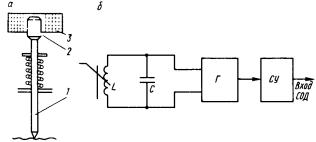

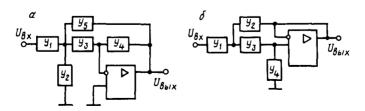

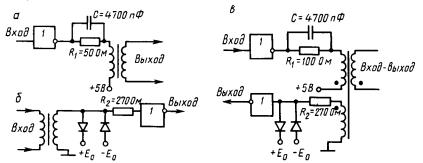

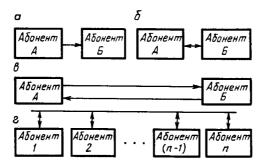

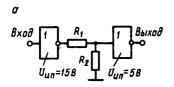

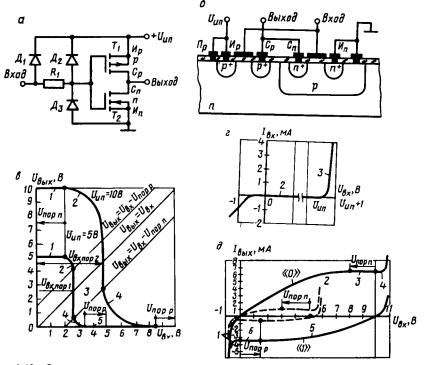

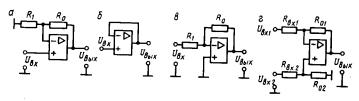

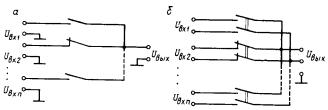

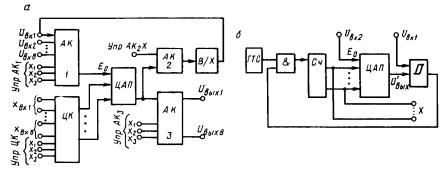

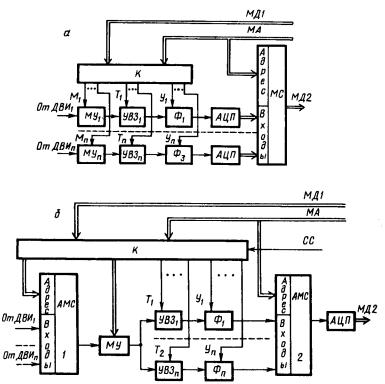

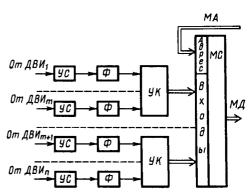

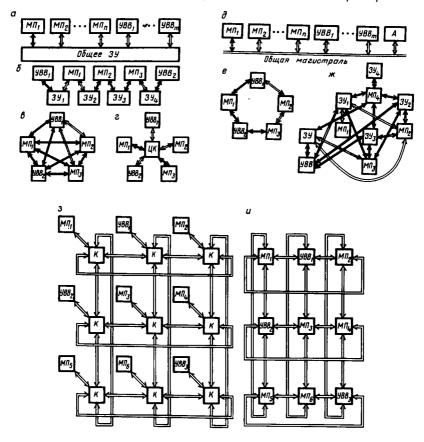

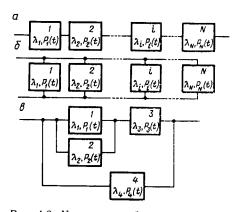

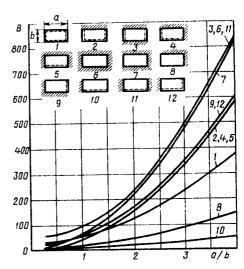

На рис. 1.2, а показана структура, реализующая принцип параллельной обработки аналоговых сигналов, поступающих от датчиков СОД. Данная структура позволяет обеспечить максимальную производительность аппаратуры всех каналов систем СОД (из-за независимости обработки каждого сигнала) и высокое качество преобразования сигналов вследствие возможности системы по обеспечению требуемого уровня нормализации сигнала на входе АЦП в каждом канале. Предельное количество каналов системы СОД в данном

Рис. 1.2. Структура системы СОД с параллельными цифровыми (a) и аналоговыми (б) выходами; с последовательными аналоговыми (в) и с последовательными и параллельными аналоговыми (г) выходами:

Д — датчик; СУ — согласующее устройство; СН — схема нормализации; ФП — функциональный преобразователь; АЦП — аналого-цифровой преобразователь; ЦМ — цифровой мультиплексор; В/Х — схема выборки — хранения; АМ — аналоговый мультиплексор; УУ — устройства управления.

случае ограничено допустимым значением динамической погрешности преобразования *i*-го параметра, т. е.

$$N_{\rm u} \leqslant \Delta x_{i,\rm gon} / \left[ (dx_i/dt)_{\rm max} t_{\rm k} \right], \tag{1.4}$$

где  $N_{\rm u}$  — предельно допустимое количество цифровых каналов преобразования системы СОД;  $\Delta x_{i\,\,{\rm доп}}$  — допустимое значение динамической погрешности i-го параметра;  $(dx_i/dt)_{\rm max}$  — максимальное значение производной i-го параметра в диапазоне преобразования;  $t_{\rm k}$  — период коммутации.

Независимость отдельных ветвей дает возможность просто (в структурном смысле) реализовать необходимые функциональные преобразования аналоговых сигналов. Большое преимущество такой системы заключается в устранении ошибок, возникающих при коммутации и выборке — хранении аналоговых сигналов, вносящих основной вклад в суммарную погрешность преобразования. Очень важно то, что эта структура позволяет значительно повысить помехозащищенность системы на основе использования цифровых каналов передачи данных на вход ЭВМ, если обеспечить преобразования сигналов непосредственно на выходе датчиков. Такой вариант построения системы сбора данных имеет большое будущее, однако на современном этапе развития микросхемотехники при его реализации имеет место более высокая стоимость СОД вследствие сравнительно высокой стоимости интегральных схем АЦП.

Другие варианты построения структуры системы СОД основаны на принципе последовательной обработки аналоговых сигналов и перенесении мультиплексирования из цифровой в аналоговую область, а также применения аналоговых схем выборки — хранения для фиксации аналоговых сигналов на входе АЦП. Это дает возможность использовать только один АЦП независимо от числа аналоговых входов, предельное количество которых можно определить из выражения

$$N_a \leqslant \Delta x_{i,\text{mon}}/[(dx_i/dt)_{\text{max}}(t_k + t_n)], \qquad (1.5)$$

где  $N_a$  — предельно допустимое количество аналоговых каналов преобразования СОД;  $t_{\pi}$  — период цикла преобразования [остальные обозначения соответствуют (1.4)].

Высокие технические характеристики свойственны структуре, приведенной на рис. 1.2,6, хорошее качество преобразования обеспечено теми же функциональными блоками, которые были включены в состав структуры, приведенной на рис. 1.2, a. Очевидно, что производительность системы сбора данных, построенной по структуре, изображенной на рис. 1.2, 6, находится в прямой зависимости от быстродействия АЦП и ограничена его динамическими параметрами, поэтому в подобных системах необходимо применять АЦП с максимальным быстродействием. Применение дополнительных элементов для обработки аналоговых сигналов мультиплексоров, схем выборки — хранения ухудшает точностные характеристики системы в це-

лом. Практически идентичными техническими характеристиками по сравнению со структурой, изображенной на рис. 1.2,  $\delta$ , обладает система сбора данных, реализованная на основе структуры, показанной на рис. 1.2, $\theta$ .

Аппаратурные затраты для реализации канала сбора данных на основе структуры, приведенной на рис. 1.2, б, будут большими по сравнению с затратами для построения канала с одной схемой выборки — хранения. Эту конфигурацию структуры наиболее рационально использовать для преобразования однократных событий.

Наиболее простой, но обеспечивающей относительно низкое качество преобразования является система, построенная по структуре, изображенной на рис. 1.2, г. Эта конфигурация структуры рациональна при условии существования сигналов высокого уровня, поступающих с датчиков системы СОД, и идентичности всех аналоговых сигналов, в этом случае можно добиться необходимого качества преобразования, сохраняя достоинства по простоте реализации.

Как правило, систему СОД в целом и систему сбора информации в частности с целью экономии средств и сокращения времени разработки наиболее рационально компоновать из отдельных блоков, реализующих функции компонентов структуры. Из анализа возможных вариантов построения структур (рис. 1.2) следует, что любой вариант реализуется на основе восьми основных функциональных устройств: датчик, схема согласования, схема нормализации, функциональный преобразователь, АЦП, цифровые мультиплексоры, аналоговые мультиплексоры, устройства управления.

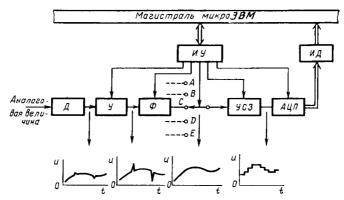

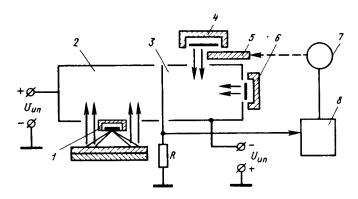

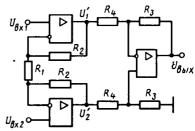

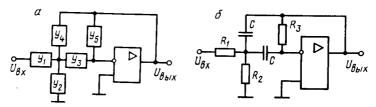

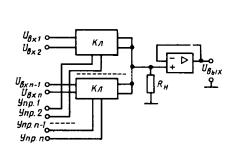

Подсистема аналогового ввода. Поскольку преобразование основных физических величин в электрические обычно не относится к функциям подсистемы аналогового ввода, ограничимся рассмотрением преобразования электрических сигналов в цифровую форму. Процесс получения аналогового сигнала с какого-либо датчика, его предварительной обработки, преобразования в цифровую форму и ввода в память ЭВМ называется сбором данных. Рис. 1.3 иллюстрирует

Рис. 1.3. Схема подсистемы аналогового ввода: ИУ — интерфейс управления; ИД — интерфейс данных.

общую схему подсистемы сбора данных. Контролируемый параметр — уровень напряжения, ток, давление, температура и т. п.— с помощью соответствующего датчика Д преобразуется в электрический сигнал. Если сигнал на выходе датчика недостаточен для последующей обработки, то он усилителем У усиливается до необходимого уровня. Далее с помощью активного фильтра Ф из сигнала удаляются нежелательные низкочастотные и высокочастотные составляющие (необходимость в предварительной фильтрации будет пояснена позднее). Отфильтрованный сигнал поступает через аналоговый мультиплексор на устройство слежения — запоминания УСЗ. Применение мультиплексора позволяет в режиме разделения времени использовать единственный аналого-цифровой преобразователь АЦП для многих каналов, экономя тем самым дорогостоящее оборудование.

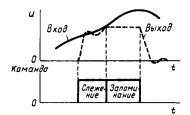

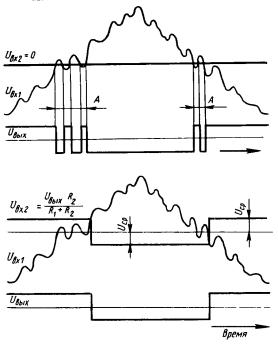

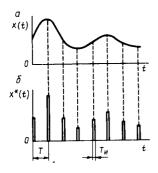

Преобразование аналоговой величины в цифровую всегда происходит за некоторый конечный промежуток времени. В течение этого промежутка времени сигнал на входе АЦП должен поддерживаться неизменным. Эту функцию выполняет устройство слежения запоминания УСЗ, сигнал на выходе которого пропорционален сигналу на входе до тех пор, пока не последует команда запоминания, после которой сигнал на выходе остается постоянным в течение промежутка времени, необходимого для преобразования сигнала в цифровую форму (рис. 1.4).

АЦП преобразует уровень напряжения на входе в соответствующую цифровую величину. Далее цифровые данные через интерфейсные схемы сопряжения поступают в общую магистраль микроЭВМ.

Рис. 1.4. Временная диаграмма работы устройства слежения — запоминания.

Из приведенной схемы сбора данных видно, что непрерывно изменяющийся входной сигнал заменяется совокупностью дискретных периодически измеренных значений, причем внутри каждого интервала амплитуда сигнала сохраняется неизменной. Процесс квантования искажает входной сигнал. Теорема Котельникова о дискретном представлении утверждает, что для точного восстановления первоначального сигнала из дискретного частота опроса должна по крайней мере вдвое превышать самую высокочастотную гармоническую составляющую входного сигнала. Частота квантования ограничена сверху скоростью работы АЦП. Время, необходимое для выполнения одного преобразования, называется апертурным. Если во входном сигнале имеются гармонические составляющие с более высокой частотой, чем частота квантования, то при восстановлении аналогового сигнала они вызовут разностные частоты более низкой часто-

ты. Для предотвращения такого искажения следует использовать фильтр нижних частот, который бы не пропускал все составляющие сигнала, имеющие частоту выше 1/2 частоты квантования. Только при этих условиях процесс квантования не вызовет потерь информации, содержащейся во входном сигнале.

Следует отметить, что из-за ограниченной разрешающей способности цифрового представления возникает также и амплитудная погрешность, которую необходимо учитывать.

В настоящее время аналоговые подсистемы выпускаются и в конструктивно законченном виде. Так, подсистема аналогового ввода фирмы «Data General» содержит плату, состоящую из двух 8-канальных мультиплексоров, усилителя с дифференциальным входом, усилителя слежения — запоминания и 12-разрядного АЦП последовательного приближения. Время преобразования составляет 33 мкс. Входные сигналы могут изменяться в диапазоне ±10 В. Фирма «Апаlog Devices Inc» производит аналоговый интерфейс, включающий в себя плату, на которой размещены усилитель с программным усилением (1—1000) и 12-разрядный АЦП.

Отечественной промышленностью выпускается модуль аналогового ввода 15 KA-60/8-010, предназначенный для преобразования напряжения постоянного тока в цифровой код и ввода его в микро-9BM «Электроника-60». Модуль имеет в своем составе мультиплексор аналоговых сигналов на 16 входов. Входы можно использовать либо как однопроводные (для 16 источников входных сигналов), либо как дифференциальные (для 8 источников входных сигналов). Имеется возможность выбора одного из двух диапазонов входных напряжений:  $\pm 1$  или  $\pm 10$  В. Напряжение на входе с помощью АЦП поразрядного уравновешивания преобразуется в 11-разрядный двоччный код (включая и знаковый разряд). Время преобразования составляет не более 100 мкс.

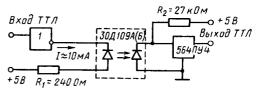

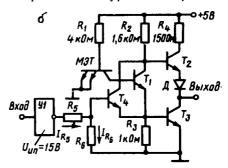

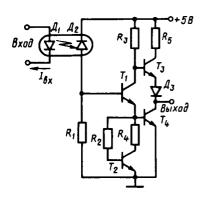

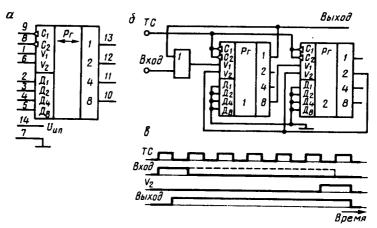

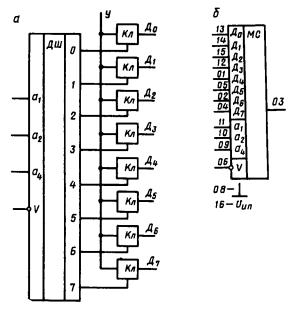

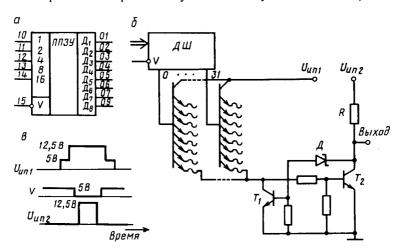

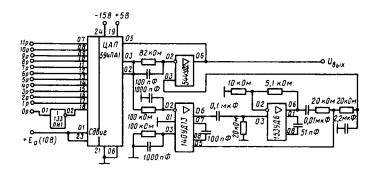

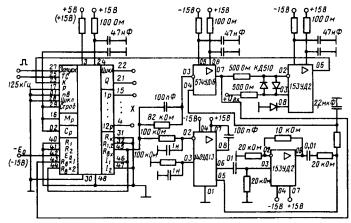

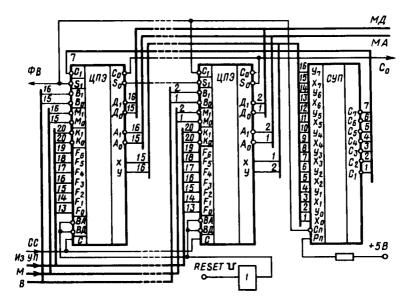

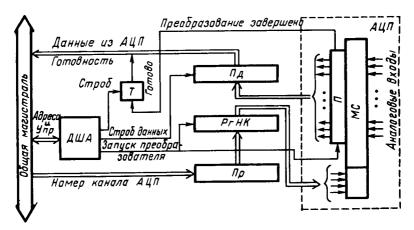

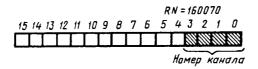

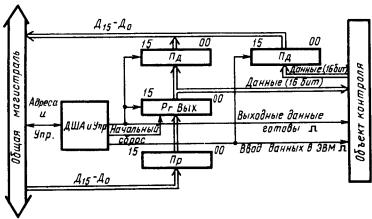

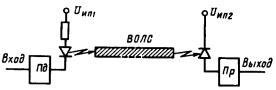

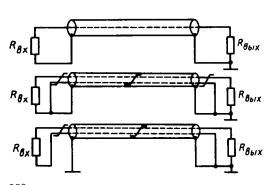

Упрощенная схема модуля аналогового ввода приведена на рис. 1.5, а, где Пд — передатчик; Пр — приемник; Т<sub>эн</sub> — триггер знака; РгДВв — регистр данных ввода; Т — триггер «Готовность»; ДША и Упр — дешифратор адреса и управляющих сигналов; СОП — схема определения полярности; АЦП — аналого-цифровой преобразователь; СУС — схема управления и синхронизации АЦП; РгДВыв регистр данных вывода; У — усилитель; МС — мультиплексор; АК адрес канала. Рассмотрим принцип его работы. Вначале с помощью программного цикла «Запись» выбирается один из входных каналов. Селектор адреса и дешифратор управляющих сигналов вырабатывают разрешающий сигнал «Вывод 0», по которому разрешается запись кода адреса выбранного канала, поступающего из магистрали микро $\ni$ BM в регистр данных вывода (биты  $\Pi_{00} - \Pi_{03}$ ). С выхода регистра код поступает на адресный вход АК мультиплексора МС. Напряжение из выбранного канала поступает на усилитель У и далее на АЦП и схему определения полярности входного сигнала СОП. Схема определения полярности позволяет упростить реализацию АЦП.

Одновременно сигнал «Вывод 0» запускает схему управления и

Рис. 1.5. Схема модуля аналогового ввода (а) и вывода (б).

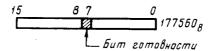

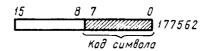

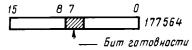

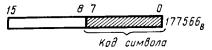

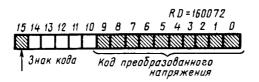

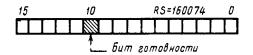

синхронизации АЦП. После завершения цикла преобразования по сигналу «Конец преобразования» устанавливается в единицу триггер Т «Готовность» (бит  $\mathcal{L}_{10}$ ). С помощью программного цикла «Чтение» состояние триггера «Готовность» может быть считано микро $\Theta$ BM (разрешающий сигнал «Ввод 4»). Прием результата преобразования в микро $\Theta$ BM осуществляется также с помощью программного цикла «Чтение», при этом вырабатывается разрешающий сигнал «Ввод 2» и через передатчики код данных ( $\mathcal{L}_{00}$  —  $\mathcal{L}_{09}$ ) и код знака ( $\mathcal{L}_{15}$ ) поступают в магистраль микро $\Theta$ BM.

Для обеспечения гальванической развязки системы питания микроЭВМ и измерительной части модуля используется изолированный источник питания. Гальваническая развязка интерфейсной части модуля и его аналоговой части осуществляется с помощью оптоэлектронных ключей.

В последнее время ряд фирм разработали устройства ввода аналоговой информации в виде гибридных микросхем. Разработаны приборы HDAS-8 (8 дифференциальных входов) и NDAS-16 (16 обычных входов), которые, кроме обязательного набора элементов, содержат

тристабильные буферные устройства для сопряжения с МД микропроцессора. Режим непрерывного сканирования обеспечивается путем коммутации внешних выводов. Устройство позволяет без значительных затрат увеличить число каналов до 256. Быстродействующие схемы выборки и хранения дают возможность анализировать в реальном масштабе времени сигналы с частотой до 25 кГц.

Разработано устройство аналогового ввода в виде КМДП прибора АДСО816. На кристалле размером 3,7×5,0 мм расположены все элементы, необходимые для стандартной системы ввода, исключая измерительные усилители. Это устройство обладает многими полезными для ввода аналоговой информации свойствами: 16-канальный мультиплексор непосредственно воспринимает любой из 16 входных сигналов, а затем либо подает этот сигнал для прямого преобразования на входную линию, либо выдает его во внешний прибор для дополнительного преобразования. Наличие регистра хранения, дешифратора адреса и тристабильных элементов упрощает сопряжение между прибором и МП.

Рассмотренные варианты построения подсистем аналогового ввода свидетельствуют о том, что их развитие идет в направлении от специализированных плат к гибридным и монолитным микросхемам. Характерная черта всех модулей — наличие средств сопряжения с микропроцессором и возможность программного выбора каналов.

Подсистема аналогового вывода. Подсистема аналогового вывода во многом похожа на подсистему аналогового ввода. В АСК подсистема аналогового вывода используется для подачи на объект контроля тестовых испытательных сигналов в виде напряжений или токов, изменяющихся во времени по заданному закону. Она может быть также применена для вывода из ЭВМ результатов контроля в виде графиков и диаграмм с помощью самописцев и графопостроителей.

Преобразование цифровых выходных данных в аналоговый сигнал выполняется с помощью ЦАП. Принцип преобразования двоичного кода в напряжение будет рассмотрен в § 1.7.

Основные трудности при создании прецизионных ЦАП возникают при изготовлении резистивных делителей.

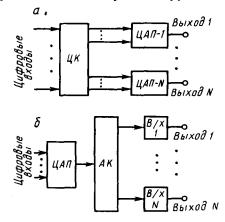

Существуют различные конфигурации подсистем аналогового вывода, однако наибольшее распространение получили подсистемы с использованием ЦАП в каждом выходном канале.

Рассмотрим подсистему аналогового вывода, построенную на базе серийно выпускаемого модуля 15KA-60/4-009 для микро9BM «Электроника-60». Модуль содержит четыре параллельных канала и предназначен для преобразования цифровых данных, выдаваемых микро9BM, в напряжение постоянного тока. Упрощенная схема модуля приведена на рис. 1.5, 6. Модуль состоит из приемников Пр и передатчиков Пд магистрали; дешифратора адреса и управляющих сигналов ДША и Упр; регистров данных  $PrД_1 — PrД_4$ ; 10-разрядных UA $\Pi_1 — U$ A $\Pi_4$ ; источника опорного напряжения  $E_0$ .

Код адреса А и управляющие сигналы Упр поступают из магист-

рали микро ЭВМ через приемники Пр на дешифратор адреса и управляющих сигналов ДША и Упр, который вырабатывает один из сигналов обращения к выбранному регистру (Bывод $_i$ ). Код данных ( $Д_{00}$ —  $Q_{09}$ ) поступает на информационные входы всех регистров  $PrQ_i$ , однако запись произойдет только в выбранный регистр. С выходов регистра код поступает в ЦАП $_i$ , где преобразуется в напряжение постоянного тока. Цифровая и аналоговая части модуля гальванически развязаны с помощью оптоэлектронных ключей. Питание аналоговой части модуля осуществляется от изолирующего источника напряжения. Источник опорного напряжения  $Q_i$ 0 вырабатывает два отдельных напряжения: положительное ( $Q_i$ 10,24 B) и отрицательное ( $Q_i$ 10,24 B). По выбору с помощью перемычек можно на любой из ЦАП подать соответствующее опорное напряжение  $Q_i$ 10 и получить на выходе ЦАП напряжение нужной полярности. Двоичные разряды, их веса и соответствующие им выходные напряжения приведены ниже:

Модуль обеспечивает по любому каналу ток не более 5 мА при выходном сопротивлении не более 1 Ом. Время установления выходного напряжения не более 10 мкс.

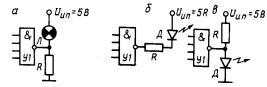

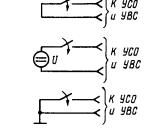

Подсистема цифрового ввода-вывода. Для АСК характерны не только аналоговые входные и выходные величины, но и величины, являющиеся по своей природе цифровыми, которые могут быть представлены двумя состояниями, например «Включено» или «Выключено», «В пределах» или «Вне пределов», «Низкий уровень» или «Высокий уровень». Кроме цифровых параметров, характеризующих состояние контролируемого объекта, существуют выходные цифровые параметры, которые задают желательное состояние объекта. Например, при контроле объекта часто возникает необходимость включения или выключения некоторых составляющих его блоков и модулей или подачи в контролируемый объект комбинаций цифровых испытательных сигналов.

Сигналы на входе, представляющие состояние контролируемого объекта, обычно имеют вид уровня напряжения, тока или состояния контактов («Замкнуто — разомкнуто»). Для сопряжения этих сигналов с ЭВМ необходимо их преобразовать в стандартные уровни. Как правило, входные цепи ЭВМ управляются ТТЛ-уровнями: «О» соответствует уровень напряжения 0—0,4 В, а «1» — уровень напряжения 2,5—5 В. В качестве преобразующих схем используют резистивные делители напряжения, диодные ограничители, компараторы, триггеры Шмитта, согласователи уровней.

Основная функция цифрового вывода — функция ключа. Обычно каждый двоичный разряд выходных цифровых данных имеет самостоятельный смысл, т. е. каждый бит выходного слова может использоваться для управления каким-либо параметром объекта независи-

мо. Выбор типа ключа определяется значением коммутируемой мощности и скорости переключения.

Электромеханические реле применяются в основном для управления сигналами средней и большой мощности при низких скоростях переключения. Они обеспечивают полную гальваническую развязку цепей.

Более надежные — полупроводниковые ключи.

Для коммутации цепей переменного тока средней и большой мощности часто используются кремниевые управляемые выпрямители.

Практически совершенными переключающими характеристиками обладают разработанные в середине 70-х годов полевые транзисторы с V-структурой (VMOS). Их отличают низкий входной управляющий ток, высокая частота переключения и значительные выходные токи. Так, мощность рассеяния прибора VN84GA составляет 90 Вт при низкой частоте переключения и 50 Вт при частоте переключения 30 МГц. Для гальванической развязки полупроводниковых ключей могут служить оптоэлектронные пары.

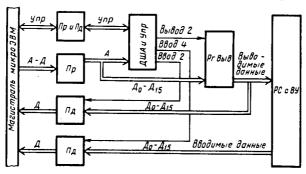

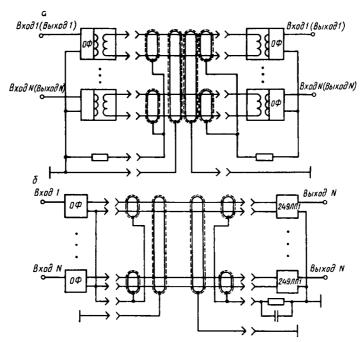

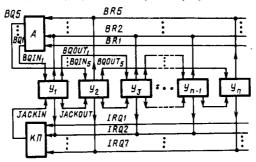

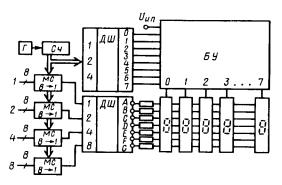

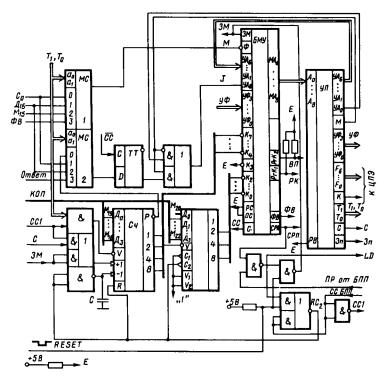

В качестве основы для построения подсистемы цифрового ввода-вывода удобно выпускаемое отечественной промышленностью устройство параллельного обмена И2 15КС-180-032. Оно предназначено для подсоединения к магистрали микроЭВМ «Электроника-60» внешних устройств, обменивающихся данными с ЭВМ в параллельном коде, и представляет собой стандартную плату, вставляемую в один из разъемов магистрали. На рис. 1.6 приведена упрощенная схема этого устройства. При рассмотрении принципов работы коснем-

Рис. 1.6. Схема модуля цифрового ввода-вывода.

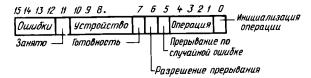

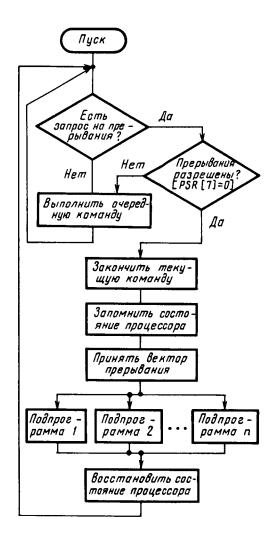

ся лишь функций, выполняемых устройством при безусловной программной передаче данных от внешнего устройства в ЭВМ и из ЭВМ во внешнее устройство. В этом случае используются два адресуемых регистра.

Для передачи данных из ЭВМ во внешнее устройство ВУ адрес регистра вывода РгВыв и управляющие сигналы Упр через приемник подаются на дешифратор адреса и управляющих сигналов ДША и Упр, который в свою очередь вырабатывает сигнал разрешения «Вывод 2». По этому сигналу происходит запись данных ( $\mathcal{L}_0$ — $\mathcal{L}_{15}$ ) в РгДВыв (данные к этому моменту присутствуют на информационных

входах регистра). С выводов регистра данные поступают на разъем связи РС с внешним устройством ВУ.

При необходимости данные, хранящиеся в регистре вывода РгДВыв, могут быть считаны программным путем. Для этой цели служат разрешающий сигнал «Ввод 2» и передатчики магистрали.

При вводе данных из внешнего устройства в ЭВМ используются адрес регистра ввода и цикл магистрали «Чтение». Следует заметить, что регистр ввода как таковой в устройстве параллельного обмена отсутствует (есть лишь его адрес). При этом вырабатывается разрешающий сигнал «Ввод 4». Вентильные схемы передатчиков открываются, и код из внешнего устройства поступает в магистраль ЭВМ. Таким образом, с помощью рассмотренного устройства можно организовать выдачу 16 управляющих сигналов в контролируемый объект, а также обеспечить прием дискретных сигналов по 16 входным каналам.

## 1.2. Датчики первичной информации

Типы датчиков. В основе организации автоматической системы ввода данных лежит применение датчиков входной информации с электрическим выходом и последующим преобразованием электрического сигнала в цифровую форму. Так как основные характеристики датчиков являются определяющими для системы сбора данных и систем управления, работающих в реальном масштабе времени, то они представляют интерес. В соответствии с измеряемым параметром удобно разделить на группы существующие датчики: измерения угловых и линейных величин; усилий, крутящих моментов, давлений, напряжений; параметров движения; измерения температуры.

Угловые размеры чаще всего ограничены 360 угл. град. В зависимости от требуемой точности измерения используют различные принципы построения преобразователей «угол — электрическая величина». Примером подобного типа преобразователей могут служить реостатные и дискретные на основе зубчатых и кодовых дисков с контактным, фотоэлектрическим или индуктивным съемом информации. Измерение угловых размеров реостатными преобразователями может быть реализовано с погрешностью 0,05—0,03 %. Возможность обеспечения большой выходной мощности значительно упрощает построение системы сбора данных. В качестве таких преобразователей применяют проволочные реостатные преобразователи с различным пределом измерения от долей одного оборота до десятков оборотов. Сопротивление преобразователя в зависимости от угла поворота

$$R_{a} = R_{\text{max}}(\alpha/\alpha_{\text{max}}) = R_{\text{max}}f(\beta), \tag{1.6}$$

где  $\beta = \alpha/\alpha_{\text{max}}$  — относительное перемещение элементов преобразователя, который при включении в электрическую цепь может быть использован в качестве косвенного преобразователя угла поворота в ток или напряжение по зависимостям

$$I_{n} = \frac{U_{0}}{R_{\alpha}} = \frac{U_{0}}{R_{\max}f(\beta)} = I_{\min}f^{-1}(\beta); U_{n} = I_{0}R_{\alpha} = I_{0}R_{\max}f(\beta) = U_{\max}f(\beta),$$

(1.7)

где  $U_0$ ,  $I_0$  — опорные напряжения и ток преобразователя.

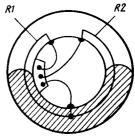

Разновидность высоконадежного реостатного датчика с неизнашивающимся контактом изображена на рис. 1.7. Поворот датчика приводит к изменению сопротивлений R1, R2, а функциональная характеристика датчика может быть записана выражением (1.7); погрешность такого преобразователя достигает 1%.

Очень часто для измерения параметров угла поворота используют вращающиеся трансформаторы (BT). На цилиндрических статоре и роторе размещаются по две обмотки, причем как обмотки статора  $\omega_e$ ,  $\omega_k$ , так и обмотки ротора  $w_s$ ,  $w_c$  сдвинуты относительно друг друга на 90 эл. град. В силу электрической перпендикулярности обмоток  $w_e$ ,  $w_k$  их воздействия на вторичные обмотки  $w_s$ ,  $w_c$  независимы и характеристика преобразования BT имеет вид

Рис. 1.7. Схема реостатного датчика.

$$U_s = K_{\tau} (U_1 \sin \alpha - U_k \cos \alpha); \ U_c = K_{\tau} (U_1 \cos \alpha + U_k \sin \alpha), \tag{1.8}$$

где  $K_{\tau} = w_s/w_e = w_c/w_k = 0, 1-1, 0$  — коэффициент трансформации ВТ;  $\alpha$  — угол поворота ротора ВТ.

Передаточные коэффициенты ненагруженного идеального ВТ изменяются по синусной или косинусной зависимости от угла поворота ротора:

$$K_{1s} = K_{\tau} \sin \alpha$$

;  $K_{1c} = K_{\tau} \cos \alpha$ ;  $K_{ks} = -K_{\tau} \cos \alpha$ ;  $K_{kc} = K_{\tau} \sin \alpha$ .

Достоинством подобных преобразователей является то, что с датчика снимаются напряжения, пропорциональные синусу и косинусу угла поворота ротора, что значительно упрощает процессы последующей обработки информации потому, что для формирования алгоритма управления чаще всего необходимы именно эти зависимости. На выходах ВТ напряжение

$$U_s = K_{\tau}U_1 \sin \alpha$$

;  $U_c = K_{\tau}U_1 \cos \alpha$  при  $U_1 = \text{const}$ ,  $U_k = 0$ .

В настоящее время все чаще используют дискретные преобразователи угол поворота — цифровой код, которые необходимы прежде всего для удовлетворения потребностей в точных измерениях угловых параметров. Цифровой выход датчика значительно упрощает ввод данных в МП вследствие отсутствия необходимости обработки аналоговых сигналов.

Как правило, в машиностроительной промышленности требуется измерять не полный диапазон заданного размера, а лишь его отклонения, которые обычно не превосходят долей миллиметра. Электрические микрометры широко применяют и обычно строят на основе электроконтактных, индуктивных и емкостных преобразователей. Шероховатость поверхности оценивается среднеквадратическим отклонением микронеровностей. Для их измерения используют осевые перемещения штока по испытуемой поверхности, которой шток касается своим заостренным наконечником. На рис. 1.8, а показана

конструкция профилографа. Датчик содержит шток 1, на его верхнем конце укреплен ферритовый стержень 2, который при движении штока изменяет индуктивность катушки 3. Электрическая схема включения профилографа приведена на рис. 1.8,  $\delta$ . Катушка

Рис. 1.8. Конструкция (а) и схема включения (б) профилографа.

профилографа L и конденсатор C образуют LC-генератор, к выходу последнего подключен частотный демодулятор. Напряжение с демодулятора поступает на вход канала сбора данных.

Примером метода измерения толщин объектов, доступных лишь с одной стороны, может служить датчик ИТП-476, в основу которого положен метод рассеянного β-излучения. Прибор (рис. 1.9) содержит три источника β-излучения 1, 4, 6, усилитель 8 и двигатель 7.

Рис. 1.9. Схема датчика для измерения толщин.

Приемник излучения представляет собой дифференциальную ионизационную камеру, состоящую из рабочей камеры 2 и компенсационной 3 с общим собирающим электродом, который через общее собирающее сопротивление R подключен к шине нулевого потенциала. Излучение радиоактивного изотопа рабочего источника I отражается от исследуемой поверхности; отраженное излучение содержит две составляющие:  $I_1$  — отражение от подложки, не зависящее от толщины покрытия,  $I_2$  — отражение от покрытия, зависящее от его

толщины. В компенсационную камеру излучение попадает от двух источников — дополнительного 6 и компенсирующего 4, которые уравновешивают в ионизационной камере составляющие  $I_1$  и  $I_2$  рабочего источника. Напряжения питания, подаваемые на корпусы камер 2 и 3, имеют противоположные знаки, поэтому результирующий ток через резистор R равен разности ионизационных токов камер, а ток регулировкой перемещения заслонки 5 может быть, при определенной отражающей способности объекта, сведен к нулю. Следовательно, угловое положение вала двигателя 7 определяет толщину покрытия. Датчик ИТП-476 позволяет измерять толщину оловянного покрытия до 5 мм и цинкового покрытия до 0,1 мм с погрешностью порядка 2 %.

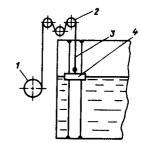

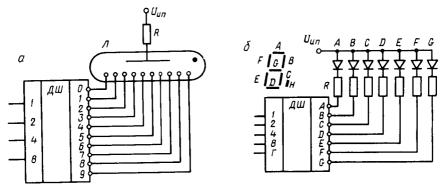

Очень часто встречается необходимость в измерениях уровней жидкости. Примером серийного датчика измерения уровня может служить серийно выпускаемый прибор УДУ-5 (рис. 1.10). Выходное напряжение датчика, пропорциональное уровню жидкости h, снима-

ется с реостатного преобразователя. Прибор УДУ-5 при пределе измерения 12 м имеет погрешность  $\pm\,15$  мм.

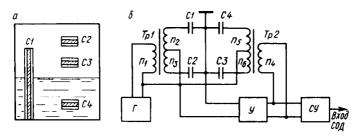

Широко используют для измерений уровня емкостные датчики. Датчик (рис. 1.11, *a*) построен на четырех коаксиаль-

Рис. 1.10. Датчик измерения уровня жидкости: I — датчик; 2 — направляющие ролики; 3 — тросик; 4 — поплавок.

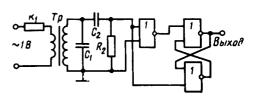

ных конденсаторах: трех компенсационных C2, C3, C4 и одном рабочем C1. Электрическая схема датчика (рис. 1.11,  $\delta$ ) содержит генератор  $\Gamma$ , усилитель V и трансформаторы Tp1, Tp2. Датчик реализует режим статического уравновешивания, значит сумма токов, поступающих на вход усилителя через емкости C1—C4, равна нулю.

Напряжение с выхода датчика пропорционально уровню жидкости.

Измерение механических напряжений и деформаций в промышленности основано на применении тензорезисторов, струнных или

Рис. 1.11. Емкостный датчик измерения уровня жидкости (а) и его схема (б).

индуктивных датчиков. Для измерений деформаций, лежащих в диапазоне от 0,005-0,002 до 1,5-2%, наиболее часто используют проволочные, фольговые, пленочные тензорезисторы при измерении механических колебаний в диапазоне от 0 до 100 к $\Gamma$ ц, так как они безынерционны.

Исследования линейных напряжений с помощью тензодатчиков методически подробно разработаны, и в основе работы тензорезисторов лежит явление тензоэффекта, заключающееся в том, что активное сопротивление проводников меняется при их механической деформации. Тензоэффект материала характеризуется коэффициентом относительной тензочувствительности  $K = \varepsilon_R/\varepsilon_l$ , где  $\varepsilon_R = \Delta R/R -$ относительное изменение сопротивления проводника;  $\varepsilon_l = \Delta l/l -$ относительное изменение длины проводника.

Конструктивно тензодатчики выполняются в виде проволочки, которая зигзагообразно наклеивается на тонкую бумагу или лаковую пленку (рис. 1.12, a), к концам проволочки припаяны медные выводы.

Рис. 1.12. Конструкция тензодатчика (а) и структура одного канала тензостанции (б).

Такой датчик приклеивается к испытуемой детали и воспринимает деформации ее поверхностного слоя. Выходной величиной тензопреобразователя является изменение его сопротивления, пропорциональное величине деформации. Кроме петлевого наклеиваемого тензодатчика для специальных исследований, разработаны и другие типы датчиков. Например, эластичные резиновые капилляры, заполненные ртутью, позволяют измерять деформации до 30—50 %.

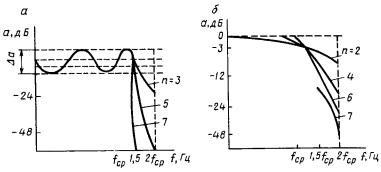

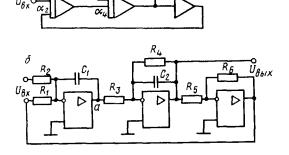

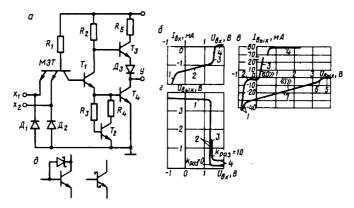

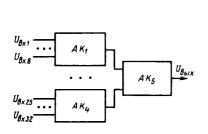

Схемы измерительных цепей тензорезисторов могут быть построены весьма разнообразно. Наиболее типичная структура одного канала тензостанции приведена на рис. 1.12, б. Измерительный мост запитан переменным напряжением генератора Г, модулированный сигнал усиливается усилителем У, демодулируется ДМ и после фильтрации поступает на обработку или фиксацию. Обычно в машиностроении исследуются деформации во многих точках; следовательно, тензостанция, как правило, многоканальна.

Тензорезисторы используют также для вторичных преобразований при измерении сосредоточенных сил и давлений в датчиках с упругими элементами. Деформация упругого элемента сплошного стержня, кольца и др., возникающая от воздействия внешней силы, изменяет сопротивление тензорезистора, которое преобразуется в электрический сигнал.

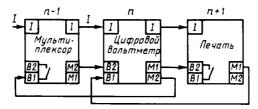

Часто СОД строят на цифровых радиоизмерительных приборах, которые в подобных системах реализуют функции датчика первичной

информации. Если к системе сбора данных не предъявляют жестких требований по габаритно-весовым характеристикам, то радиоизмерительные приборы (генераторы сигналов) используют для формирования сигналов манипуляции внутренним состоянием объекта управления или измерения. Для применения в СОД радиоизмерительные приборы должны иметь цифровые выходы для считывания информации и цифровые входы управления режимами работы. Отечественная промышленность выпускает широкую номенклатуру такого типа радиоизмерительных приборов. Например, универсальный вольтметр В7-30 предназначен для измерения постоянного и синусоидального напряжений, сопротивления постоянному току, отношения постоянных напряжений, отношения синусоидального напряжения к постоянному, мгновенного значения входного напряжения в режиме выборки-хранения, работы с каналом коллективного пользования. Вольтметр обеспечивает измерение постоянного напряжения двух полярностей на пределах 0,1; 10; 100; 1000 В; измерение среднеквадратического значения синусоидального напряжения до 500 В в диапазоне частот от 20 Гц до 100 кГц. Возможность автоматического управления процессом измерения с регистрацией данных и наличие в вольтметре блока сопряжения с каналом коллективного использования обеспечивает возможность широкого применения его в СОЛ.

Малые постоянные напряжения измеряют вольтметром постоянного тока B2-36, который имеет диапазон измерений 0,05 мкВ — 19,999 В. Дистанционное управление запуском цикла измерения, выбор поддиапазонов измерений и цифровой выход позволяют использовать вольтметр в СОД.

Измерение медленно меняющихся напряжений, токов и малых зарядов от источников с высоким выходным сопротивлением реализует универсальный вольтметр В7-34, который обладает дистанционным управлением процесса измерения и цифровым выходом.

Цифровая информация вольтметров выдается в коде 8—4—2—1. Широко применяют в СОД частотомеры, которые предназначены для автоматического измерения частоты электрических колебаний с высокой разрешающей способностью. Одно из основных требований к аппаратуре частотомера при включении его в состав системы сбора данных — это обеспечение возможности дистанционного управления и цифрового выхода. Подобными характеристиками обладает большинство частотомеров, выпускаемых промышленностью, например Ч3-55.

В системах сбора данных используют генератор импульсов Г5-79, генератор низкочастотный Г3-110 с программатором 321, высокочастотные генераторы Г4-141, Г4-155, Г4-156, генератор сигналов специальной формы Г6-33. Генератор импульсов Г5-79 предназначен для формирования серий прямоугольных импульсов и линейно-ступенчатых сигналов различной формы, при этом обеспечивается регулировка амплитуды, длительности, периода повторения импульсов в серии и периода повторения серий импульсов, полярности, базового смещения, временного сдвига. Схема управления генератора

обеспечивает возможность записи и хранения программы воспроизве-

дения заданной последовательности импульсов.

Комплект генератора ГЗ-110 с программатором 321 формирует синусоидальные электрические колебания с высокой точностью и стабильностью частоты в диапазоне 0,01 Гц—2 мГц (дискретно через 0,01 Гц). Возможность программното управления позволяет приме-

нять его в системах сбора данных.

Высокочастотные генераторы сигналов Г4-14, Г4-185, Г4-156 контролируют радиоаппаратуру и другие средства связи, работающие в режимах АМ, ЧМ и комбинированной АМ/ЧМ. Дистанционное управление работой генераторов в цифровом коде позволяет реализовать точную установку параметров генерируемого сигнала при включении их в состав СОД, причем генераторы Г4-155, 156 имеют внутреннюю оперативную память для хранения 16 наборов частот и уровней мощности.

Для исследования, настройки и испытаний радиоэлектронных устройств систем автоматического управления удобно использовать генератор Г6-33. Генератор предназначен для формирования сигналов синусоидальной, треугольной, пилообразной, пилообразно-импульсной и прямоугольной формы с переменной скважностью, высокой точностью и стабильностью по частоте. Диапазон частот 0,001—10 000 Гц, управление прибором возможно от ЭВМ, при этом программируются все параметры сигналов: частота, форма, ослабление, фазовый сдвиг.

Из краткого рассмотрения отдельных датчиков исходной информации, применяемых в СОД, видно, что параметры выхода датчиков весьма многообразны, но в самом общем виде их можно разделить на аналоговые и цифровые. Такое разделение позволяет определить основные задачи преобразования сигналов, поступающих на вход СЭД, и конкретизировать схему всей системы сбора и обработки данных.

Из рассмотрения типов и конструкций датчиков следует, что характеристики выходных цепей и сигналов очень разнообразны, но с целью рационального построения системы сбора данных можно распределить параметры выхода датчиков по группам в соответствии с формой несущего сигнала табл. 1.1. Анализируя таблицу, выделяем требования по сопряжению датчика с входом канала сбора данных.

Преобразования сигналов, снимаемых с датчиков. Процесс преобразования аналоговых сигналов в цифровые, кроме процедуры преобразования, включает в себя операции обработки аналоговых устройств СОД. Операции обработки аналоговых сигналов определяются требованием обеспечения заданного качества сигнала и в отдельных случаях необходимостью проведения определенных функциональных преобразований.

Большинство датчиков СОД имеют большое выходное сопротивление и малый динамический диапазон, поэтому необходимо согласование параметров выхода датчиков с параметрами входных цепей системы обработки данных. В качестве согласующих устройств широ-

|                                                     | Групп                                                                                       | ы датчиков, объединенные                                                                                                            | Группы датчиков, объединенные по форме выходного сигнала                                                                                                 | ла                                                                                                      |                                                                                       |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Характеристики                                      | аналоговые                                                                                  | говые                                                                                                                               |                                                                                                                                                          | дискретные                                                                                              |                                                                                       |

| дагчика                                             | Постоянное<br>напряжение<br>(ток)                                                           | Переменное<br>напряжение<br>(ток)                                                                                                   | Цифровой<br>код                                                                                                                                          | Частота<br>следовання<br>импульса                                                                       | Относительная<br>длительность                                                         |

| 1                                                   | 2                                                                                           | 3                                                                                                                                   | 4                                                                                                                                                        | ഹ                                                                                                       | 9                                                                                     |

| Функция преобразования $U_{	ext{вых}} = k lpha [B]$ | $U_{_{\mathrm{BMX}}}=k lpha[\mathrm{B}]$                                                    | $u_{\text{BMX}} = A \sin(\omega_0 \times X + \varphi_0)$ $A = U_0[1 + m\lambda]$                                                    | $X_{\mathtt{Bhx}} = k \lambda [\mathrm{eд. \ KOдa}]$                                                                                                     | $F_{\text{BHX}} = k \alpha  [\Gamma u]$                                                                 | $Q_{\text{BHX}} = k\alpha$                                                            |

| Смещение нулевого уров- $U_{cM} = A [MB]$           | $U_{\text{CM}} = A  [\text{MB}]$                                                            |                                                                                                                                     | X <sub>см</sub> = x <sub>0</sub> [ед. кода]                                                                                                              | $F_{ m cm} = F_0 \left[ \Gamma { m u}  ight]$                                                           | $Q_{ m cM} = Q_0$                                                                     |

| Чувствительность S                                  | $\frac{dU_{\text{BMX}}}{d\alpha} \left[ \frac{B}{1 + \Phi, B} \right]$                      | $\frac{dA}{d\lambda} \left[ \frac{B}{1 + B} \right]$                                                                                | $\frac{dX}{d\alpha} \left[ \begin{array}{cc} \text{ел. кода} \\ \hline 1 & \phi. & \text{в} \end{array} \right]$                                         | $\frac{dF}{d\alpha} \left[ \begin{array}{c} \Gamma_{\rm LL} \\ 1 & \Phi. & {\rm B} \end{array} \right]$ | $\frac{dQ}{d\alpha} \left[ \frac{1}{1 \ \phi. \ B} \right]$                           |

| Диапазон преобразова-<br>ния:<br>рабочий<br>полный  | $U_{\rm pa6}[-U_{\rm pa6},+ \ +U_{ m pa6}][{ m B}] \ U_{ m n}[-U_{ m n},+U_{ m n}][{ m B}]$ | $u_{\mathrm{pa6}}[-u_{\mathrm{pa6}},+ u_{\mathrm{pa6}}] + u_{\mathrm{pa6}}[B] = u_{\mathrm{n}}[-u_{\mathrm{n}},+u_{\mathrm{n}}][B]$ | $X_{\text{pa6}} [-X_{\text{pa6}}, + + X_{\text{pa6}}] [\text{e.r. kona}]$ $X_{\text{n}} [-X_{\text{n}}, + X_{\text{n}}] [\text{e.g.}]$ $X_{\text{nona}}$ | $F_{ m pao}[-F_{ m pao},+\ +F_{ m pao}][\Gamma u] \ F_{ m n}[-F_{ m n},+F_{ m n}][\Gamma u]$            | $Q_{\rm pa6} [-Q_{\rm pa6}, + Q_{\rm pa6}] $<br>$Q_{\rm n} [-Q_{\rm n}, + Q_{\rm n}]$ |

| Время установления т,<br>мкс                        | T                                                                                           | l                                                                                                                                   | 7                                                                                                                                                        | T                                                                                                       | Ţ                                                                                     |

Окончание табл. 1.1

| $\frac{a}{U_{\text{BMX}}} \left[ \frac{1  \phi.  B}{B} \right]$                                                       |

|-----------------------------------------------------------------------------------------------------------------------|

|                                                                                                                       |

| + +                                                                                                                   |

| $v_{\text{max}} = \frac{\Delta \alpha}{\Delta t} \left[ \frac{1  \phi  B}{C} \right] \qquad \omega_0 = C  [\Gamma u]$ |

кое применение нашли операционные усилители, которые ставят на входе аналоговых устройств СОД.

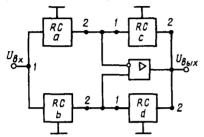

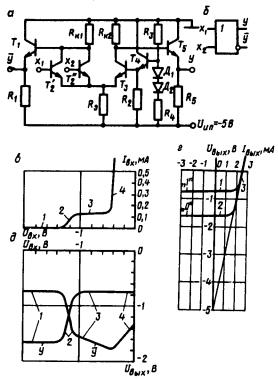

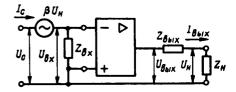

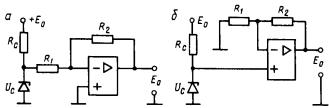

Формирование схемы включения операционного усилителя для решения поставленной задачи зависит от требуемого качества сигнала. Для оценки качества усиления сигнала при условии воздействия помех хорошим критерием является определение отношения сигнал/ шум. Наиболее рационально использовать схему согласующего устройства, приведенную на рис. 1.13, входное сопротивление которой  $R_{\rm BX} = R_{\rm BX,V} (1+K_{\rm V}\beta) \approx 10^{10}$  Ом, где  $\beta = R_1/(R_1+R_2)$ .

Рис. 1.13. Схема согласующего устройства канала системы СОД.

### Из выражений

$$\begin{split} &U_{\text{BX}1}' \! = \! -U_{\text{BX}2}(R_2/R_1) \! + \! U_{\text{BX}1}(1 \! + \! R_2/R_1); \ U_{\text{BX}2}' \! = \! -U_{\text{BX}1}'(R_2/R_1) \! + \! U_{\text{BX}2}(1 \! + \! R_2/R_1); \\ &U_{\text{BX}1}' \! - \! U_{\text{BX}2}' \! = \! (U_{\text{BX}1} \! - \! U_{\text{BX}2}) + (U_{\text{BX}1} \! - \! U_{\text{BX}2}) \ (2R_2/R_1); \\ &U_{\text{BMX}} \! = \! - (U_{\text{BX}1}' \! - \! U_{\text{BX}2}') \ (R_3/R_4), \end{split}$$

а следовательно,  $U_{\text{вых}} = -\left[ (U_{\text{вх 1}} - U_{\text{вх 2}}) + (U_{\text{вх 1}} - U_{\text{вх 2}})(2R_2/R_1) \right] \times$ находим коэффициент усиления дифференциальногс  $\times (R_3/R_4)$ сигнала:

$$|K_{\text{диф}}| = U_{\text{вых}}/(U_{\text{вх 1}} - U_{\text{вх 2}}) = (1 + 2R_2/R_1) (R_3/R_4).$$

В соответствии с определением степень подавления синфазной помехи  $KOCC = K_{\text{диф}}/K_{\text{синф}}$ , поэтому в данной схеме можно достичь значительного ослабления синфазной составляющей сигнала-помехи. Высокое входное сопротивление, возможность получения больших коэффициентов усиления и КОСС во многих случаях делают предпочтительным выбор указанной схемы для реализации согласующего устройства системы СОД. В этом можно убедиться на следующем примере.

Пусть максимальное значение сигнала с датчика будет 10 мВ, требуемый динамический диапазон входа АЦП 10 В, синфазная помеха  $U_{\text{п. синф}} = 3$  В, тогда необходимый коэффициент усиления равен  $10^3$ , а коэффициент ослабления синфазного сигнала

$$KOCC = \frac{1}{\delta} \frac{U_{\text{п.син}\phi}}{U_{\text{вx}}} = \frac{1}{0.01} \frac{3}{10 \cdot 10^{-3}},$$

(1.9)

где δ — допустимая относительная приведенная погрешность от возлействия помехи (здесь 1 %).

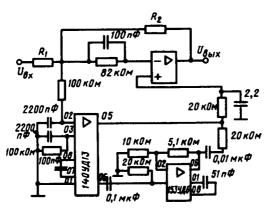

Для реализации схемы выбираем операционный усилитель 153УД6, резисторы ОМЛТ 5 %, коэффициент передачи выходного каскада принимаем равным единице. Для усилителя 153УД6  $KOCC_{o.v.} \approx 2 \cdot 10^4$ .

Для всего согласующего устройства значение коэффициента ослабления КОСС СУ =  $KOCC_1 \cdot KOCC_2 \geqslant 3 \cdot 10^4$ , где  $KOCC_1 \geqslant 3 \cdot 10^3$ ;  $KOCC_2 = K_{\text{диф}}/K_{\text{синф}} = 10$ ;  $K_{\text{диф}} = 1$ ;  $K_{\text{синф}}$  для схемы выходного каскада согласующего устройства зависит главным образом от неточности изготовления резисторов  $R_3$ ,  $R_4$ ; для выбранной схемы  $K_{\text{синф}} \approx 2\delta_r/100 = 2 \cdot 5/100 = 0,1$ .

Для входного каскада  $K_{\text{синф}} = 1$ ,  $K_{\text{диф}} = 3 \cdot 10^3$ ,  $R_1 = 1$  кОм, тогда  $R_2 = 1,5$  мОм. Принимаем  $R_3 = R_4 = 15$  кОм. Реальные значения коэффициентов ослабления несколько меньше:

$$\begin{split} & \mathsf{KOCC}_1^\mathsf{p} = \mathsf{KOCC}_1 \cdot \mathsf{KOCC}_{o,y,} / \left( \mathsf{KOCC}_1^\mathsf{q} + \mathsf{KOCC}_{o,y} \right) = 2,7 \cdot 10^3; \\ & \mathsf{KOCC}_2^\mathsf{p} = \mathsf{KOCC}_2^\mathsf{q} \cdot \mathsf{KOCC}_{o,y} / \left( \mathsf{KOCC}_2^\mathsf{q} + \mathsf{KOCC}_{o,y} \right) = 9,9; \\ & \mathsf{KOCC}_{c,y}^\mathsf{p} = \mathsf{KOCC}_1^\mathsf{p} \cdot \mathsf{KOCC}_2^\mathsf{p} = 2,67 \cdot 10^4. \end{split}$$

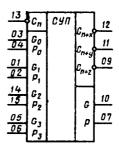

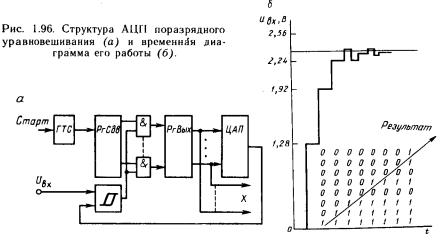

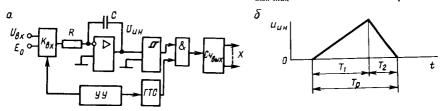

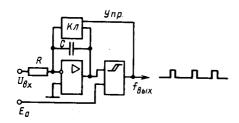

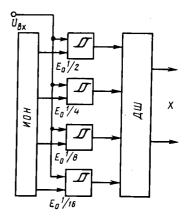

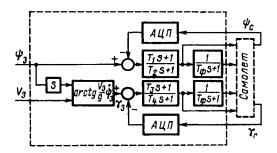

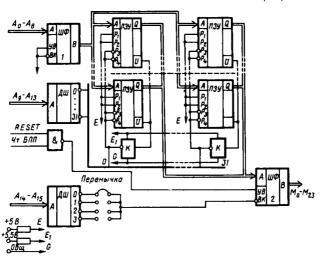

Функциональные преобразования аналогового сигнала проводят с целью введения в структуру датчика блоков для воспроизведения определенных математических операций и повышения его точностных параметров. Поясним сказанное на примерах. Измерение скорости потока жидкости или газа основано на применении датчиков перепада давления в двух точках потока P. В этом случае скорость потока  $v = \sqrt{2g\Delta P}$ .